周波数シンセサイザ市場:タイプ別(フラクショナルN、フラクション/インテジャーハイブリッド、インテジャーN)、テクノロジー別(DDS、PLL、信号発生器)、周波数範囲別、用途別、流通チャネル別-2025-2032年のグローバル予測

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

## 周波数シンセサイザ市場:詳細分析(2025-2032年)

### 市場概要

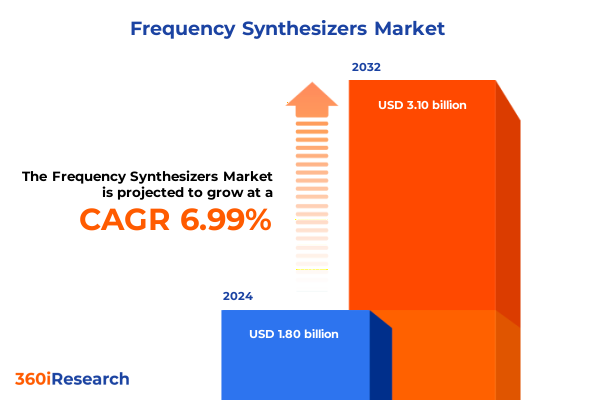

周波数シンセサイザ市場は、2024年に18.0億米ドルと推定され、2025年には19.3億米ドルに達すると予測されています。その後、年平均成長率(CAGR)6.99%で成長し、2032年までに31.0億米ドル規模に達すると見込まれています。周波数シンセサイザは、現代の通信および電子システムにおいて、精密なタイミング、安定した通信リンク、高性能な信号生成を可能にする上で極めて重要な役割を担っています。最新のワイヤレスネットワークからレーダーシステム、消費者向けデバイスに至るまで、正確な周波数制御を必要とするほぼすべてのアプリケーションにおいて、これらのコンポーネントは「心臓部」として機能します。

近年、より高いデータスループット、低遅延接続、そしてますます小型化されるフォームファクタに対する要求が加速しており、周波数シンセサイザの革新は半導体およびシステム設計戦略の最前線に押し上げられています。このため、技術イネーブラー、アーキテクチャ上のトレードオフ、およびアプリケーション固有の性能要件に関する深い理解が、技術リーダーやシステムインテグレーターにとって不可欠となっています。位相ロックループ(PLL)、直接デジタルシンセシス(DDS)、および新たに登場した分数/整数ハイブリッドアプローチを基盤として、現代の周波数シンセサイザは複数の機能を統合し、基板スペースの合理化と電力効率の向上を実現しています。これらのハイブリッドソリューションは、5Gインフラ、衛星通信、および先進レーダーシステムによって課される、ますます厳格な位相ノイズ、スプリアスエミッション、およびロックダウン要件に対応しています。同時に、スマートフォンやウェアラブルデバイスなどの消費者向けエレクトロニクス分野では、マルチバンドサポートと超低消費電力をコンパクトなフットプリントで両立させる機能が求められています。

### 推進要因

周波数シンセサイザ市場の成長は、複数の主要な推進要因によって支えられています。

**1. 先端技術の進化と統合:**

デジタル信号処理、シリコン統合、および先進材料科学の融合は、周波数シンセサイザ開発に革新的な時代をもたらしています。設計者は、従来の整数-Nおよび分数-Nシンセサイザを超え、直接デジタルシンセシスの精度を微細な周波数ステップに活用しつつ、位相ロックループの安定性を粗いチューニングに利用するハイブリッド分数/整数トポロジーを採用する傾向が強まっています。このシフトにより、より広範な性能仕様を満たし、同時に基板レベルの設計複雑性を簡素化できる新しいクラスのソリューションが実現しています。

同時に、小型化とエネルギー効率の高い動作への推進は、無線周波数フロントエンド機能、低ノイズ乗算段、およびオンチップ校正エンジンの統合を促進しています。このようなシステムオンチップ(SoC)アーキテクチャは、部品表(BOM)を削減し、航空宇宙通信から消費者向けエレクトロニクスに至るアプリケーションの市場投入までの時間を短縮します。さらに、ミリ波5G展開と車載レーダーシステムの普及は、超広帯域周波数カバレッジに重点を置き、設計チームを先進半導体プロセスを採用し、全デジタル位相ロックループやノイズシェーピング分数シンセサイザなどの斬新なアーキテクチャを探索するよう促しています。

並行して、デジタルツイン、シミュレーション駆動型設計、および機械学習を活用したチューニングワークフローの普及が、開発ライフサイクルを再構築しています。インサイチュ(in situ)パラメータ抽出に基づくデジタル校正プロトコルは、外部試験装置への依存を減らし、プロトタイプの検証を加速し、歩留まりを向上させています。これらの技術およびプロセス革新は、周波数シンセサイザ設計における画期的な瞬間を画し、前例のないレベルの性能、統合、および製造可能性を推進しています。

**2. 2025年米国関税政策の影響:**

2025年に米国が特定の半導体輸入に課した改定関税は、グローバルサプライチェーンとコスト構造に複雑な層を導入しました。影響を受ける地域の重要な知的財産および専門的なシリコンファウンドリサービスに依存するメーカーは、着地コストの増加に直面し、調達戦略の戦略的再評価を促しました。これらの関税調整は、一部の統合デバイスベンダーが国内生産能力の拡大を加速し、関税フリーの貿易協定を含むサプライヤーネットワークを多様化したため、リードタイムに波及効果をもたらしました。その結果、設計チームは部品表の構成を再評価し、主要コンポーネントのマルチソーシングに移行し、高周波ミキサー段および電圧制御発振器モジュール用の在庫バッファを優先しています。

いくつかの業界プレーヤーは、国境を越えた関税負債への露出を軽減するため、現地での組み立ておよび試験施設への投資を加速しました。このようなニアショアリングの取り組みは、輸送リスクを低減し、設計改訂および品質フィードバックループへの応答性を向上させるという追加の利点を提供します。これらの進展はまた、システムインテグレーターとコンポーネントベンダー間の協力的な対話を促進し、より透明性の高いコスト転嫁メカニズムを確立するよう促しました。長期契約に関税転嫁条項を組み込み、関税還付プログラムを探索することで、ステークホルダーは予測可能な価格設定を確保し、プロジェクトのタイムラインをより厳密に管理できます。関税情勢が進化し続ける中、プロアクティブなサプライチェーンオーケストレーションは、性能目標を維持し、プロジェクトマージンを保護するために不可欠となるでしょう。

**3. 市場セグメンテーションによる成長機会:**

* **タイプ別:** 従来の分数-Nシンセサイザは周波数分解能と位相ノイズのバランスを保ち、整数-Nアプローチはシンプルなループ動作と堅牢なスプリアス制御を求めるアプリケーションで引き続き好まれています。しかし、分数/整数ハイブリッドアーキテクチャは、ワイヤレスインフラや電子戦プラットフォームにおける動的な帯域幅要件に対応できる多用途なソリューションとして台頭しています。

* **技術別:** 直接デジタルシンセシス(DDS)は、高速周波数ホッピングとアジャイル変調フォーマットを可能にし、しばしばソフトウェア定義無線(SDR)アプリケーションの基盤となります。対照的に、位相ロックループ(PLL)エンジンは、商用電気通信システムの主力であり、セルラー基地局向けに安定したロック時間と低ジッターをサポートします。周波数シンセシス段と振幅・位相変調経路を組み合わせた信号発生器モジュールは、生産テストおよび校正プロセスを合理化するためにますます統合されています。

* **周波数範囲別:** 500 MHz未満で動作する周波数シンセサイザは産業オートメーションおよび試験計測分野に、500 MHzから1 GHzの範囲はコアワイヤレスインフラおよび衛星ダウンリンクに対応します。1 GHzから2 GHzの帯域は初期の5Gサブ6展開と連携し、2 GHzを超える製品はミリ波バックホールリンクおよび車載レーダー向けに最適化されています。

* **アプリケーション別:** 航空宇宙および防衛分野のエンドユーザーは、通信システムの相互運用性、電子戦の回復力、およびレーダーの精度を優先します。自動車システムは、先進運転支援システム(ADAS)向けに車載グレードの信頼性と温度ドリフト制御を要求します。スマートフォン、タブレット、ウェアラブルなどの消費者向けデバイスは、超コンパクトなフットプリントと電力最適化が必要です。産業用途は過酷な環境での堅牢な動作を目標とし、電気通信インフラは5G展開、マイクロ波バックホール、および衛星アップリンク性能のために設計されたソリューションに依存しています。

**4. 地域市場のダイナミクス:**

* **アメリカ:** 米国は国内半導体製造および組み立てを支援するインセンティブを通じて能力拡大を推進しており、カナダの成長する5Gインフラプロジェクトと航空宇宙クラスターは、堅牢で高精度の周波数シンセサイザソリューションへの需要を刺激しています。ラテンアメリカの電気通信近代化プログラムは、費用対効果の高いシステム向けに新たな市場を徐々に開拓していますが、急速な更新サイクルよりも長期的なサービス信頼性を優先し続けています。

* **ヨーロッパ、中東、アフリカ (EMEA):** 西ヨーロッパ諸国は厳格な規制基準と安全な通信ネットワークへの注力でリードしています。中東の衛星通信および防衛近代化への投資増加は、高周波、低位相ノイズの周波数シンセサイザに対する要件を生み出しています。対照的に、一部のアフリカ市場は、接続ギャップを埋めるための手頃でスケーラブルなワイヤレスアクセスソリューションを重視しており、エントリーレベルの周波数シンセサイザプラットフォームにとって肥沃な土壌を提供しています。

* **アジア太平洋:** 急速な都市化、政府支援のチップセット開発イニシアチブ、および広範なモバイル展開が、地域および多国籍ベンダー間の激しい競争を刺激しています。中国の半導体製造における自給自足へのコミットメントは、多数の国産周波数シンセサイザ設計を触媒しており、日本と韓国は成熟したプロセス技術を活用して、先進レーダーおよび衛星システム向けに超高周波製品を提供しています。インドの急成長するエレクトロニクス組み立て部門は、少量生産の特殊モジュールと大量生産の消費者向けデバイスコンポーネントの両方にとって費用対効果の高いハブとして台頭しています。

### 展望と戦略的提言

業界リーダーは、広帯域カバレッジと低位相ノイズという二重の要件に対応するため、分数/整数シンセシス技術と直接デジタル制御を統合するハイブリッドアーキテクチャ開発への投資を優先すべきです。ミリ波通信や先進レーダー、自動車用LiDAR、衛星メガコンステレーションリンクなどの新興セグメントにおける新たな標準に研究開発ロードマップを合わせることで、組織は先行者利益を確保できます。さらに、企業は関税の変動や物流のボトルネックから生産タイムラインを保護するため、地域ファウンドリ能力や代替流通チャネルを含むサプライヤー関係を多様化する必要があります。地域のアセンブリパートナーとの戦略的協力は、フィードバックループを短縮し、反復的な設計改善と地域に特化した品質保証プロセスを可能にします。同時に、AI駆動型チューニング、インサイチュ校正、および高度なシミュレーションレイヤーを通じた内部ワークフローのデジタル変革は、プロトタイピングまでの時間を短縮し、開発コストを削減するでしょう。最後に、マーケティングおよび営業チームは、初期のシステムモデリングから現場での性能最適化に至るまで、エンドツーエンドの統合サポートを強調する価値提案を策定すべきです。IPコアの柔軟なライセンスモデルと量産向けの拡張可能なサポートパッケージを提供することで、業界プレーヤーは大手OEMと新興イノベーターの両方に対応できます。このような顧客中心のアプローチは、技術的卓越性とサプライチェーンの回復力に裏打ちされ、周波数シンセサイザの次なるアプリケーションの波を捉える上で業界リーダーを有利な立場に置くでしょう。

以下に、ご指定の「周波数シンセサイザ」という用語を正確に使用し、詳細な階層構造で目次を日本語に翻訳します。

—

## 目次

1. **序文**

* 市場セグメンテーションと範囲

* 調査対象期間

* 通貨

* 言語

* ステークホルダー

2. **調査方法**

3. **エグゼクティブサマリー**

4. **市場概要**

5. **市場インサイト**

* 衛星通信トランシーバー向けに最適化された低位相ノイズPLLアーキテクチャの展開

* 高速ADCを活用した直接RFサンプリング向けデジタル専用**周波数シンセサイザ**の登場

* 超低消費電力IoTセンサーノードを可能にするエネルギー効率の高いCMOSベースシンセサイザの採用

* 高精度アプリケーションにおけるサブHz分解能のためのフォトニック周波数コムジェネレータの統合

* ソフトウェア定義無線およびレーダープラットフォームをサポートするためのチップレット上のマルチチャネルデジタルPLLの使用

* 5G NR FR2および車載レーダーシステム向けミリ波SiGe BiCMOSシンセサイザの開発

* 過酷な環境下での安定した周波数生成のためのオンチップ温度補償DCOの実装

6. **2025年米国関税の累積的影響**

7. **202

………… (以下省略)

*** 本調査レポートに関するお問い合わせ ***

周波数シンセサイザは、現代の電子工学において極めて重要な役割を担う装置であり、安定した基準周波数から、高精度かつ柔軟に様々な周波数を生成する技術の総称です。無線通信、レーダー、計測器、コンピュータのクロック生成など、その応用範囲は広範にわたり、我々の日常生活を支える多くの電子機器に不可欠な要素となっています。従来のLC発振器や水晶発振器が特定の高安定周波数を生成するものの、周波数可変性や広範囲での安定性に限界があったのに対し、周波数シンセサイザはこれらの課題を克服し、広範囲にわたる周波数を水晶発振器に匹敵する安定性で提供することを可能にしました。

主要な周波数シンセサイザの方式は、大きく分けて「直接デジタルシンセサイザ(DDS)」と「位相同期ループ(PLL)シンセサイザ」の二つが挙げられます。DDSは、デジタル技術を用いて周波数を生成する方式であり、位相アキュムレータ、ルックアップテーブル、D/Aコンバータを主要な構成要素とします。その最大の利点は、非常に細かい周波数分解能と高速な周波数切り替え速度にあり、デジタル制御による高い柔軟性を提供します。しかし、高周波数帯域での利用や、スプリアスと呼ばれる不要な信号の発生において課題を抱える場合があるため、用途に応じた設計が求められます。

一方、PLLシンセサイザは、基準周波数と電圧制御発振器(VCO)の出力周波数を比較し、その位相差を検出してVCOの周波数を制御するフィードバックループを利用します。その主要な構成要素は、位相比較器、ループフィルタ、電圧制御発振器(VCO)、そして分周器です。この方式は、高周波数帯域での動作が可能であり、優れた位相ノイズ特性を実現しやすいという利点があります。しかし、周波数切り替え速度はループフィルタの特性に依存するため、DDSに比べて遅くなる傾向があります。また、周波数分解能は基準周波数と分周比によって決まるため、高分解能を得るためには工夫が必要です。

これらのシンセサイザの性能を評価する上で重要な指標は多岐にわたります。まず、「周波数分解能」は、生成できる最小の周波数ステップを指し、DDSでは非常に細かく設定可能です。次に、「周波数切り替え速度」は、ある周波数から別の周波数へ移行し、安定した出力が得られるまでの時間を示します。また、「位相ノイズ」は、出力信号のスペクトル純度を表すもので、通信システムの品質に直結する極めて重要な要素です。さらに、「スプリアス」と呼ばれる不要な信号の発生レベルも、シンセサイザの性能を測る上で厳しく評価されます。

周波数シンセサイザは、移動体通信における基地局や携帯電話、Wi-Fiルーター、GPS受信機、衛星通信、さらにはレーダーシステムや医療機器のMRIなど、我々の日常生活に深く浸透しています。計測器分野では、高精度な信号発生器やスペクトラムアナライザの局部発振器として不可欠であり、コンピュータの分野では、CPUのクロック生成にも利用され、システムの安定動作を支えています。近年では、5G/6G通信、高分解能レーダー、量子コンピュータといった次世代技術の進展に伴い、より高周波数帯域への対応、低消費電力化、小型化、そしてさらなる位相ノイズの低減が強く求められています。これらの技術的課題を克服し、より高性能で汎用性の高い周波数シンセサイザの開発が、今後もエレクトロニクス産業の発展を牽引していくことでしょう。