世界のPCIeスイッチチップ市場:製品タイプ別 (統合型スイッチ、スタンドアロン型スイッチ)、テクノロジー別 (Gen 3、Gen 4、Gen 5)、ポート数別、アーキテクチャ別、用途別、エンドユーザー別 – 2025-2032年グローバル予測

※本ページの内容は、英文レポートの概要および目次を日本語に自動翻訳したものです。最終レポートの内容と異なる場合があります。英文レポートの詳細および購入方法につきましては、お問い合わせください。

*** 本調査レポートに関するお問い合わせ ***

PCIeスイッチチップ市場は、次世代コンピューティングの相互接続アーキテクチャの基盤として、その重要性を増しています。Peripheral Component Interconnect Express (PCIe) スイッチチップは、CPU、GPU、アクセラレータ、ストレージデバイス間の高速かつ低遅延のデータパスを可能にする、現代のコンピューティングインフラストラクチャにおいて不可欠な存在です。PCI-SIGによって定義されたPCIeは、2003年の登場以来、進化を続け、第6世代ではレーンあたり最大64 GT/sの速度をサポートし、以前のバージョンとの後方互換性を維持しています。PCIeスイッチチップによる複数のエンドポイントのオーケストレーションは、スループットを犠牲にすることなく接続性を効果的に増幅させ、人工知能(AI)、機械学習(ML)、ハイパースケールデータセンターにおけるデータ集約型ワークロードを強力に支援しています。

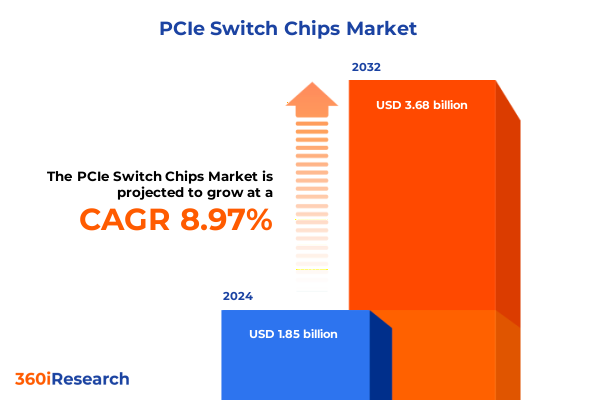

市場規模に関して、PCIeスイッチチップ市場は2024年に18.5億米ドルと推定され、2025年には19.7億米ドルに達すると予測されています。その後、年平均成長率(CAGR)8.97%で成長し、2032年までに36.8億米ドルに達すると見込まれており、この成長は、技術革新とデータ処理需要の増大に強く牽引されています。

PCIeスイッチチップ市場の成長は、主に技術的進歩、アプリケーション需要の進化、および地域ごとの動向によって推進されています。技術的進歩の面では、PCIeスイッチチップの状況は、世代間の進歩と補完的な相互接続規格の統合によって変革的な変化を遂げています。PCIe 5.0の登場により、データレートはレーンあたり32 GT/sに倍増し、帯域幅の新たなベンチマークを設定し、機械学習クラスターやストレージファブリックにおける前例のないレベルのコンポーザビリティを可能にしました。この勢いはPCIe 6.0の採用を加速させ、64 GT/sの速度、前方誤り訂正(FEC)、および電力効率の向上を導入することで、AIトレーニング環境の新たな性能閾値を解き放っています。同時に、Compute Express Link (CXL) とPCIeスイッチアーキテクチャの融合は、データセンターにおけるメモリプーリングとコヒーレンシモデルを再構築し始めています。CXL強化型スイッチは、プロセッサとアクセラレータ間のキャッシュコヒーレント通信を可能にすることで、異種システム全体で遅延を削減し、メモリ利用率を向上させています。このハイブリッド相互接続の統合は、オペレーターが動的なワークロードをサポートするためにより大きな柔軟性とリソースコンポーザビリティを求める中で、インフラストラクチャ設計を再定義するとされています。これらの変化は、相互接続アーキテクチャがもはや静的な導管ではなく、進化する性能要求に適応するますますインテリジェントなファブリックであるという広範なトレンドを強調しています。

進化するデータセンター需要とアプリケーションも重要な推進要因です。AI、機械学習、ハイパースケールデータセンターといったデータ集約型ワークロードの増加は、PCIeスイッチチップに対する需要を強力に押し上げています。自動車システムでは、先進運転支援システム(ADAS)機能をサポートするためにPCIeスイッチチップの統合が進み、コンシューマーエレクトロニクスでは高度なマルチメディア処理に利用されています。データセンターやエンタープライズサーバーでは、これらのスイッチは高スループットのネットワークアダプタやNVMeストレージファブリックを支え、ネットワーキング機器ではノンブロッキング性能を実現するためにクロスバーアーキテクチャを活用しています。ストレージ中心のプラットフォームでは、コストと遅延のバランスを取る共有バス設計が優先され、両方のアプローチの強みを統合するハイブリッドアーキテクチャが登場しています。

地政学的要因とサプライチェーンの課題も市場に影響を与えています。2025年初頭の米国政府による関税措置は、PCIeスイッチチップおよびその上流コンポーネントの調達において複雑さをもたらしました。2025年1月1日には、中国からの半導体輸入に対する関税が25%から50%に倍増し、部品調達に大きなコスト圧力をかけました。これを受けて、多くのバイヤーは既存の注文を加速させたり、サプライヤーポートフォリオを多様化したりして、利益率の低下を緩和しようとしました。その後、2025年4月2日に発令された「解放記念日」の大統領令は、ほぼすべての輸入品に10%の基本関税を課し、さらに2025年4月5日からは中国製品に対して最大34%の国別相互関税を課しました。これによりサプライチェーンの混乱はさらに悪化しましたが、わずか数週間後の2025年5月28日、米国国際貿易裁判所はこれらの広範な関税が大統領権限を超えていると判断し、その執行に対する恒久的な差し止め命令を出しました。このような急速な政策変動は、サプライヤーとの関係や在庫戦略に負担をかけ、ステークホルダーにアジャイルな調達フレームワークの導入やニアショアリングの選択肢の検討を促しました。差し止め命令が出されたにもかかわらず、貿易摩擦の再燃や将来の関税調整の可能性は、設備投資、製造拠点、および長期的なサプライチェーンのレジリエンス戦略に引き続き影響を与えています。

PCIeスイッチチップ市場の展望は、技術の進化、多様なセグメンテーション、競争環境、そして戦略的推奨事項によって形成されています。主要なセグメンテーションとして、製品タイプではハイパースケールデータセンター向けの高ポート数一体型スイッチから、産業用およびIoT向け堅牢な2~4ポートバリアント、ODM(Original Design Manufacturer)/OEM(Original Equipment Manufacturer)向けのスタンドアロン型、さらにはソフトウェア定義型バリアントまで多岐にわたります。

以下に、ご指定の「PCIeスイッチチップ」という用語を正確に使用し、詳細な階層構造で目次を日本語に翻訳します。

—

**目次**

* **序文**

* 市場セグメンテーションと対象範囲

* 調査対象期間

* 通貨

* 言語

* ステークホルダー

* **調査方法**

* **エグゼクティブサマリー**

* **市場概要**

* **市場インサイト**

* スループットとスケーラビリティ向上のためのデータセンターサーバーにおけるPCIe 5.0スイッチチップの統合

* 高速アプリケーションにおける電気信号完全性の制限を克服するための光PCIeスイッチモジュールの採用

* エンタープライズおよびクラウドインフラストラクチャにおける仮想化のためのマルチルートPCIeスイッチアーキテクチャの開発

* 高頻度取引および金融コンピューティングにおける低遅延PCIeバイファケーションスイッチの需要増加

* エッジコンピューティングにおけるカスタマイズ可能なデータパス管理のためのプログラマブルFPGAベースPCIeスイッチソリューションの成長

* ヘテロジニアスコンピューティングプラットフォーム向けPCIeスイッチチップとAIアクセラレータの統合という新たなトレンド

* コンパクトなネットワーク機器における熱制約に対処する電力効率の高いPCIeスイッチ設計の進歩

* サードパーティ製PCIeスイッチコントローラとホ

………… (以下省略)

*** 本調査レポートに関するお問い合わせ ***

現代のコンピューティングシステムにおいて、高速なデータ転送と多様な周辺機器の接続は不可欠であり、その基盤を支える技術の一つがPCI Express(PCIe)である。PCIeは、CPUとGPU、SSD、ネットワークカードといった高性能デバイス間を結ぶシリアルインターフェースのデファクトスタンダードとして広く普及している。しかし、CPUが直接接続できるPCIeレーン数には物理的な限界があり、また、複数のデバイスが効率的に帯域幅を共有し、柔軟なシステム構成を実現するためには、単なるポイント・ツー・ポイント接続だけでは不十分となる。ここで中心的な役割を果たすのが、PCIeスイッチチップである。このチップは、複数のPCIeデバイスをホストCPUに接続するための仲介役として機能し、システムの拡張性、柔軟性、そして性能を飛躍的に向上させる。

PCIeは、差動信号を用いた高速なシリアル通信プロトコルであり、レーンと呼ばれる独立した送受信ペアの集合体で構成される。x1、x4、x8、x16といったレーン幅があり、世代が進むごとに各レーンの転送速度が倍増していくため、PCIe Gen4やGen5といった最新世代では膨大な帯域幅が提供される。しかし、CPUが持つPCIeコントローラは、限られた数のレーンしか提供できない。例えば、サーバー向けCPUであっても、利用可能なレーン数は数十本程度に留まることが一般的である。高性能GPUを複数搭載するシステムや、大量のNVMe SSDを接続するストレージシステム、あるいは多数のネットワークインターフェースを必要とするデータセンター環境では、このCPU直結のレーン数では到底賄いきれない。PCIeスイッチチップは、この制約を克服し、CPUの限られたレーンを複数のダウンストリームポートに分配することで、より多くのデバイスを接続可能にする。これにより、システム設計者は、必要なデバイス数や帯域幅に応じて柔軟なトポロジーを構築できるようになる。

PCIeスイッチチップの内部構造は、アップストリームポートと複数のダウンストリームポート、そしてそれらを結ぶ内部ルーティングロジックから構成される。アップストリームポートはホストCPUまたは上位のPCIeスイッチに接続され、ダウンストリームポートには各種エンドポイントデバイスや下位のPCIeスイッチが接続される。スイッチチップは、受信したPCIeパケットのヘッダ情報を解析し、適切なダウンストリームポートへ転送するルーティング機能を担う。この際、単にパケットを転送するだけでなく、Quality of Service(QoS)機能によって特定のデバイスやデータフローに優先順位を付けたり、エラー検出・訂正機能によってデータ転送の信頼性を高めたりすることも可能である。また、ホットプラグ機能に対応することで、システムの稼働中にデバイスの抜き差しを安全に行えるようにし、システムの可用性を向上させる。さらに、SR-IOV(Single Root I/O Virtualization)のような仮想化支援機能を搭載するスイッチチップもあり、これにより物理的なPCIeデバイスを複数の仮想マシンで共有し、I/O性能を向上させることができる。電力管理機能も重要な要素であり、ASPM(Active State Power Management)などを通じて、アイドル状態のデバイスやリンクの消費電力を削減し、システム全体のエネルギー効率を高める。

PCIeスイッチチップの応用分野は多岐にわたる。コンシューマー向けのマザーボードでは、CPUの限られたレーンから複数のM.2スロットや拡張スロットにPCIeレーンを供給するために利用されることがある。一方、エンタープライズ分野ではその重要性がさらに増す。データセンターのサーバーでは、複数の高性能GPUをAI/MLワークロードのために接続したり、大量のNVMe SSDを高速ストレージプールとして構成したりする際に、PCIeスイッチが不可欠となる。例えば、1Uサーバーに24台以上のNVMe SSDを搭載する場合、CPU直結のレーンだけでは物理的に接続できないため、PCIeスイッチを介してレーンを拡張する必要がある。また、FPGAアクセラレーターや高速ネットワークインターフェースカード(NIC)を多数利用するHPC(High Performance Computing)環境や、産業用PC、組み込みシステムにおいても、PCIeスイッチはシステムの柔軟性と拡張性を確保する上で中心的な役割を担っている。

技術の進化に伴い、PCIeスイッチチップにはさらなる高性能化が求められている。PCIe Gen5、そして将来のGen6といった次世代インターフェースへの対応は、より高い帯域幅と低レイテンシを実現するために不可欠である。これに伴い、スイッチチップ内部のルーティング能力や信号品質の維持、そして消費電力の最適化が重要な課題となる。また、CXL(Compute Express Link)のような新たなインターフェース技術との連携も注目されている。CXLはPCIe物理層を基盤としつつ、メモリコヒーレンシをサポートすることで、CPUとアクセラレーター間でのメモリ共有を可能にする。PCIeスイッチチップがCXLトラフィックのルーティングをサポートすることで、より柔軟で高性能な異種混合コンピューティング環境の構築が期待される。ソフトウェア定義型インフラストラクチャの進展も、PCIeスイッチの役割を変化させる可能性がある。よりインテリジェントなスイッチング機能や、リソースの動的な割り当て、監視機能などが求められるようになるだろう。

このように、PCIeスイッチチップは、現代のコンピューティングシステムにおいて、単なるデータ転送の仲介役を超え、システムの拡張性、柔軟性、性能、そしてエネルギー効率を決定づける重要なコンポーネントである。その進化は、AI、ビッグデータ、クラウドコンピューティングといった先端技術の発展を支え、今後の情報社会の基盤を形成し続けるであろう。